# Dependability Modeling with the Architecture Analysis & Design Language (AADL)

Peter Feiler (Software Engineering Institute) Ana Rugina (LAAS-CNRS)

**July 2007**

CMU/SEI-2007-TN-043

**Performance-Critical Systems Initiative**

Unlimited distribution subject to the copyright.

This report was prepared for the

SEI Administrative Agent ESC/XPK 5 Eglin Street Hanscom AFB, MA 01731-2100

The ideas and findings in this report should not be construed as an official DoD position. It is published in the interest of scientific and technical information exchange.

This work is sponsored by the U.S. Department of Defense. The Software Engineering Institute is a federally funded research and development center sponsored by the U.S. Department of Defense.

Copyright 2007 Carnegie Mellon University.

#### NO WARRANTY

THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

Use of any trademarks in this report is not intended in any way to infringe on the rights of the trademark holder.

Internal use. Permission to reproduce this document and to prepare derivative works from this document for internal use is granted, provided the copyright and "No Warranty" statements are included with all reproductions and derivative works.

External use. Requests for permission to reproduce this document or prepare derivative works of this document for external and commercial use should be addressed to the SEI Licensing Agent.

This work was created in the performance of Federal Government Contract Number FA8721-05-C-0003 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center. The Government of the United States has a royalty-free government-purpose license to use, duplicate, or disclose the work, in whole or in part and in any manner, and to have or permit others to do so, for government purposes pursuant to the copyright license under the clause at 252.227-7013.

For information about purchasing paper copies of SEI reports, please visit the publications portion of our Web site (http://www.sei.cmu.edu/publications/pubweb.html).

# **Table of Contents**

| Abst | bstract |          |                                                                         |          |  |

|------|---------|----------|-------------------------------------------------------------------------|----------|--|

| 1    | Intro   | duction  | 1                                                                       | 1        |  |

| 2    | Dep     | endabili | ity Modeling with the Error Model Annex                                 | 2        |  |

| 3    | The     | AADL A   | Architecture Model                                                      | 4        |  |

| 4    | Reus    | sable Eı | rror Models                                                             | 6        |  |

|      | 4.1     | Error N  | Model Definition                                                        | 6        |  |

|      | 4.2     | Error N  | Model Annex Libraries                                                   | 8        |  |

|      | 4.3     | Examp    | ples of Error Model Definitions                                         | 8        |  |

|      |         | 4.3.1    | Fault and Repair Models for an Isolated Component                       | 9        |  |

|      |         | 4.3.2    | Modeling Transient and Permanent Faults                                 | 11       |  |

|      |         | 4.3.3    | Modeling Error Propagation                                              | 12       |  |

|      |         | 4.3.4    | General Error Model for Hardware Components                             | 15       |  |

|      |         | 4.3.5    | General Error Model for Software Components                             | 18       |  |

|      |         | 4.3.6    | Comparison of General Error Models for Hardware and Software Components | 20       |  |

| 5    | -       |          | hitectures and Error Models                                             | 21       |  |

|      | 5.1     |          | iation of Error Model Instances                                         | 21       |  |

|      | 5.2     | Error F  | Propagations between Components of the System                           | 23       |  |

|      |         | 5.2.1    | Dependency Rules for Propagations                                       | 23       |  |

|      |         | 5.2.2    | Inheritance Rules for Propagations                                      | 26       |  |

|      | 5.3     |          | Propagation across Error Models                                         | 27       |  |

|      | 5.4     | Filterin | ng of Incoming Propagations                                             | 28       |  |

|      |         | 5.4.1    | Role of a Guard_In Property                                             | 28       |  |

|      |         |          | Guard_In Property Application                                           | 28       |  |

|      |         |          | Error Propagation Mappings                                              | 30       |  |

|      |         | 5.4.4    | Error Propagation Filtering and Masking                                 | 32       |  |

|      |         | 5.4.5    | Connection-Specific Filtering                                           | 33       |  |

|      | 5.5     |          | ng of Outgoing Propagations                                             | 33       |  |

|      |         | 5.5.1    | Role of a Guard_Out property                                            | 33       |  |

|      |         | 5.5.2    | Guard_Out Property Application                                          | 34       |  |

|      |         |          | Error Propagation Pass-Through Mappings                                 | 36       |  |

|      | 5.6     |          | Pass-Through Filtering and Masking State Propagation                    | 38<br>39 |  |

|      | 5.0     |          |                                                                         |          |  |

|      |         | 5.6.1    | Use of Error States in Conditions Use of Inferred Error States          | 39       |  |

|      | 5.7     | 5.6.2    | arison between Guard_In and Guard_Out                                   | 40<br>41 |  |

|      |         | _        |                                                                         | 41       |  |

| 6    | •       |          | ance Error Models                                                       | 42       |  |

|      | 6.1     | Abstra   | action with Basic Error Models                                          | 42       |  |

|      |         | 6.1.1    | When to Use Basic Error Models                                          | 43       |  |

|      |         | 6.1.2    | How to Use Basic Error Models                                           | 43       |  |

|      | 6.2     | Derive   | ed Error Models                                                         | 44       |  |

| Refe | ferences 76 |                |                                                                 |          |

|------|-------------|----------------|-----------------------------------------------------------------|----------|

| 10   | Sum         | mary           |                                                                 | 75       |

| 9    | Anal        | lysis Re       | eport Information                                               | 74       |

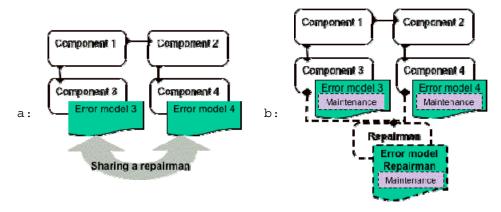

| 8    | Mod         | eling M        | aintenance and Repair                                           | 72       |

|      |             | 7.5.6          | Mutually Observing Components                                   | 69       |

|      |             | 7.5.5          | Mutually Informing Components                                   | 67       |

|      |             | 7.5.4          | A Monitoring Component                                          | 64       |

|      |             | 7.5.3          | Self-Managing Components                                        | 62       |

|      |             | 7.5.2          | Hot Standby of Self-Observing Components                        | 59       |

|      |             | 7.5.1          | Cold Standby of Self-Observing Components                       | 57       |

|      | 7.5         | AADL           | Model Examples for Systems with Modes                           | 57       |

|      | 7.4         |                | Transitions and Error Models                                    | 56       |

|      |             | 7.3.3          | How to Specify Error-Based Mode Transition Conditions           | 55       |

|      |             | 7.3.1          | How to Specify Event-Based Mode Transition Conditions           | 54       |

|      |             | 7.3.1          | Role of a Guard_Transition Property                             | 53       |

|      | 7.3         | _              | Transition Logic                                                | 53       |

|      |             | 7.2.2          | How to Use Guard_Event Properties                               | 51       |

|      |             | 7.2.1<br>7.2.2 | Role of a Guard_Event Property Guard_Event Property Application | 50<br>51 |

|      | 7.2         |                | ration of System Events                                         | 50       |

|      | 7.0         | 7.1.2          | Application of Modes and Events                                 | 49       |

|      |             | 7.1.1          | Modes, Mode Transitions, and Events                             | 49       |

|      | 7.1         |                | ling of Operational Modes                                       | 49       |

| 7    | -           |                | I Modes and Error States                                        | 48       |

|      |             |                |                                                                 |          |

|      |             | 6.2.2          | How to Use Derived Error Models                                 | 45       |

|      |             | 6.2.1          | When to Use Derived Error Models                                | 45       |

# List of Figures

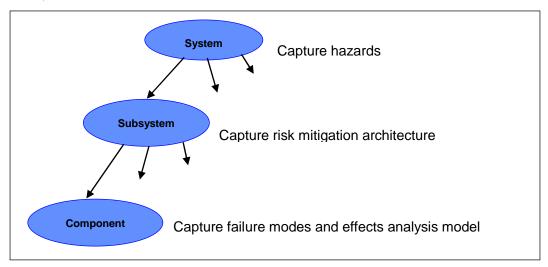

| Figure 1:  | Error Models in System Hierarchy                      | 2  |

|------------|-------------------------------------------------------|----|

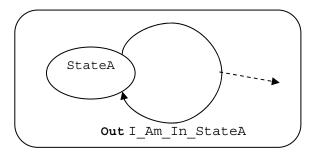

| Figure 2:  | State Visible from Outside                            | 15 |

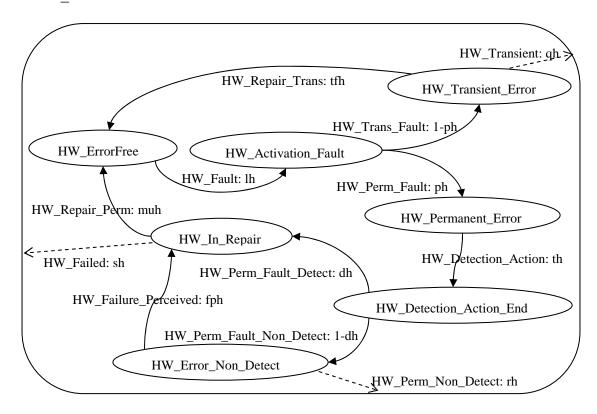

| Figure 3:  | General Hardware Component Error Model                | 16 |

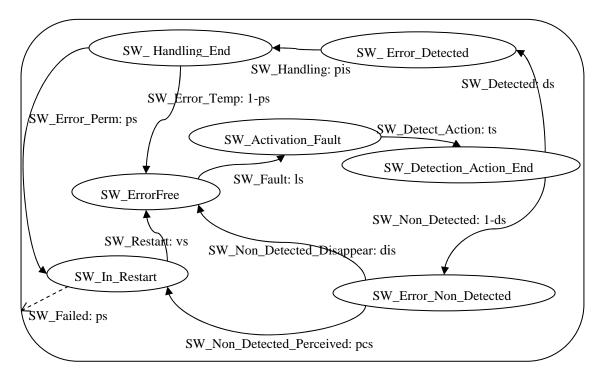

| Figure 4:  | General Software Component Error Model                | 19 |

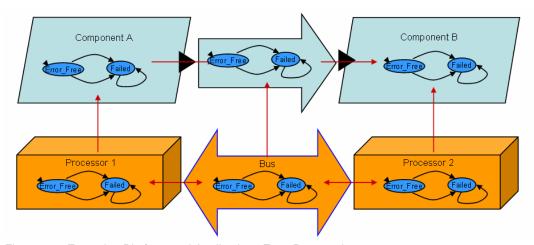

| Figure 5:  | Execution Platform and Applications Error Propagation | 25 |

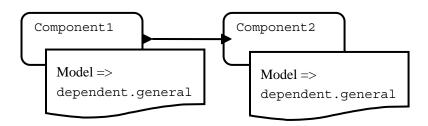

| Figure 6:  | End-to-End Propagation                                | 27 |

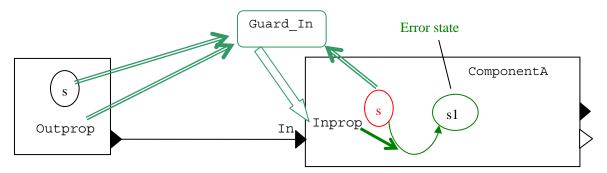

| Figure 7:  | Guard_In Mapping                                      | 29 |

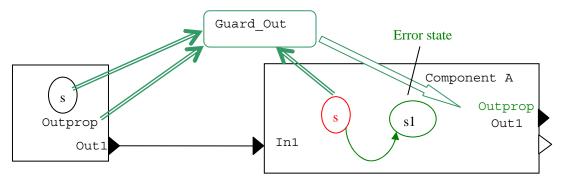

| Figure 8:  | Guard_Out Mapping                                     | 34 |

| Figure 9:  | AADL Architecture with Guard_Out Property             | 38 |

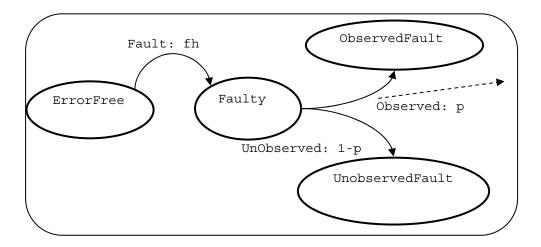

| Figure 10: | Observed Fault                                        | 41 |

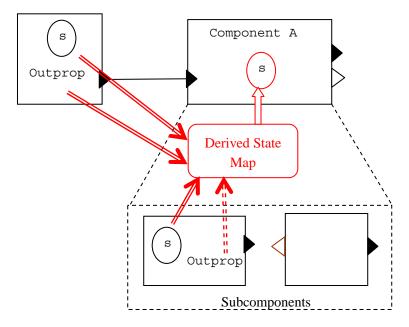

| Figure 11: | Derived Error State Mapping                           | 45 |

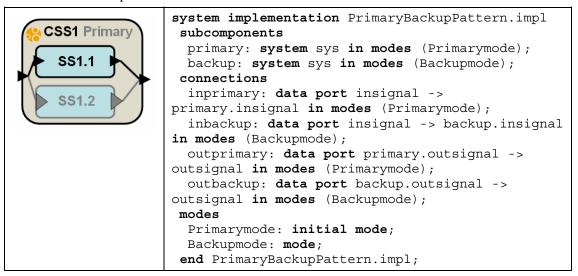

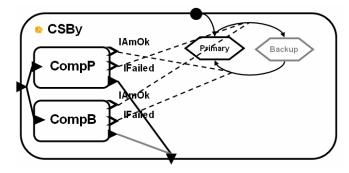

| Figure 12: | Dual Redundancy Pattern                               | 50 |

| Figure 13: | Cold Standby Pattern                                  | 58 |

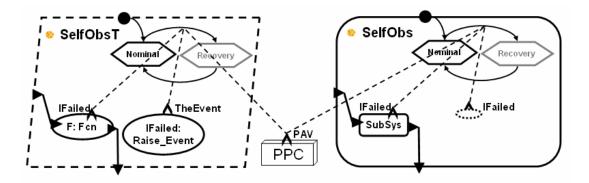

| Figure 14: | Cold Standby of a Self-Observing Component            | 58 |

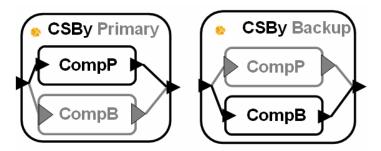

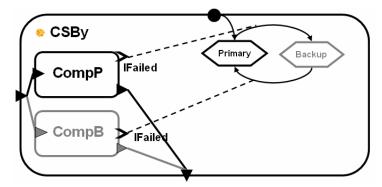

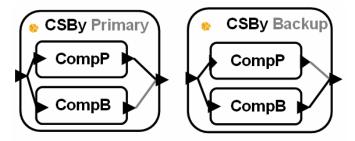

| Figure 15: | Hot Standby Pattern                                   | 60 |

| Figure 16: | Hot Standby of a Self-Observing Component             | 60 |

| Figure 17: | A Self-Managing Component                             | 63 |

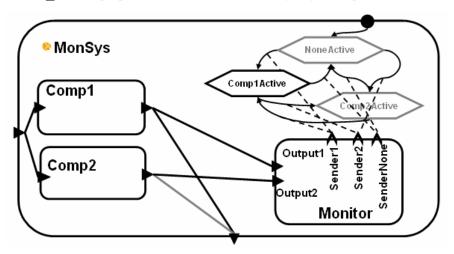

| Figure 18: | Monitoring Component                                  | 65 |

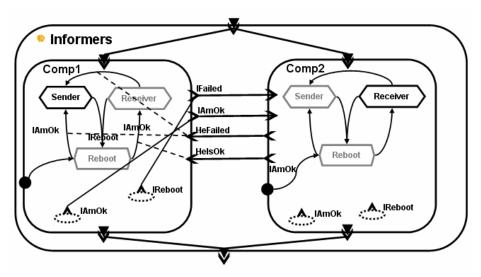

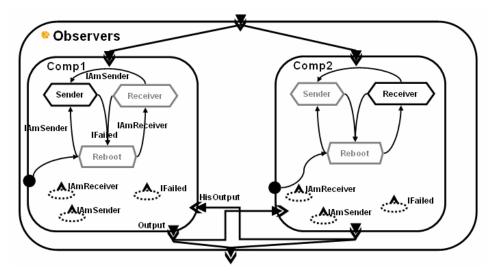

| Figure 19: | Mutually Informing Components                         | 67 |

| Figure 20: | Mutually Observing Components                         | 69 |

| Figure 21: | Maintenance Dependency                                | 72 |

# List of Tables

| Table 1:  | Content in this Document                                    | 1  |

|-----------|-------------------------------------------------------------|----|

| Table 2:  | Error Model Definition                                      | 6  |

| Table 3:  | Error Model Annex Library                                   | 8  |

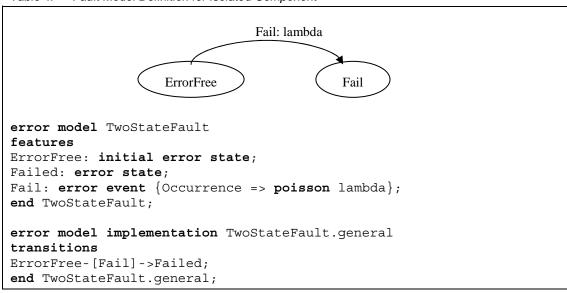

| Table 4:  | Fault Model Definition for Isolated Component               | 9  |

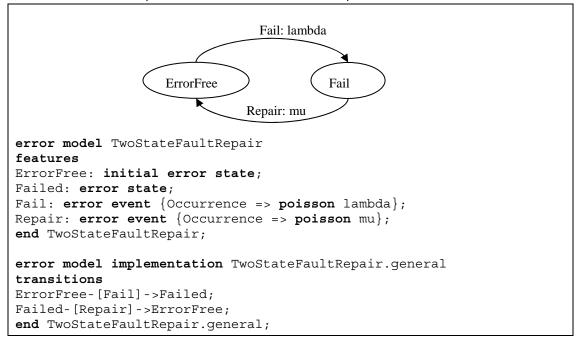

| Table 5:  | Fault and Repair Model Definition for Isolated Component    | 10 |

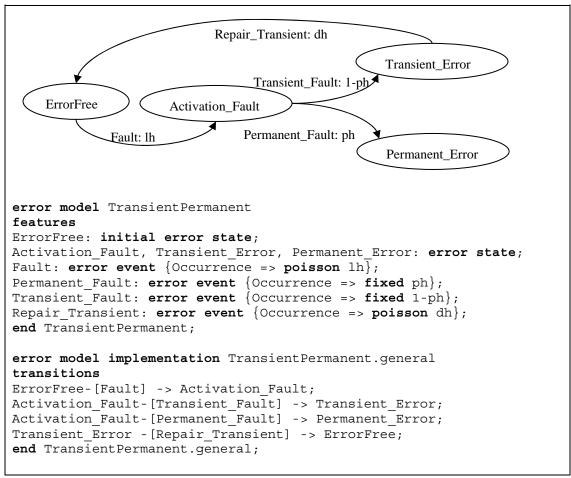

| Table 6:  | Fault Model with Transient and Permanent Faults             | 11 |

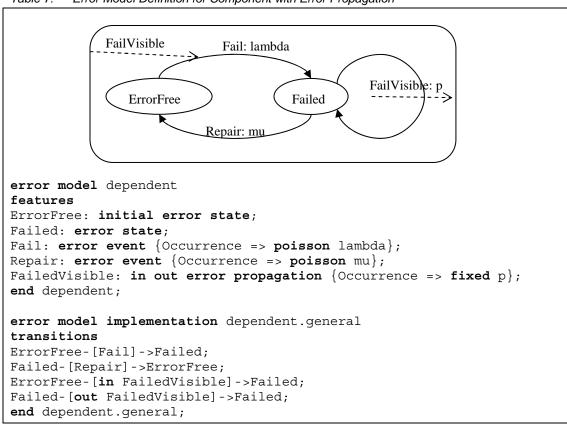

| Table 7:  | Error Model Definition for Component with Error Propagation | 13 |

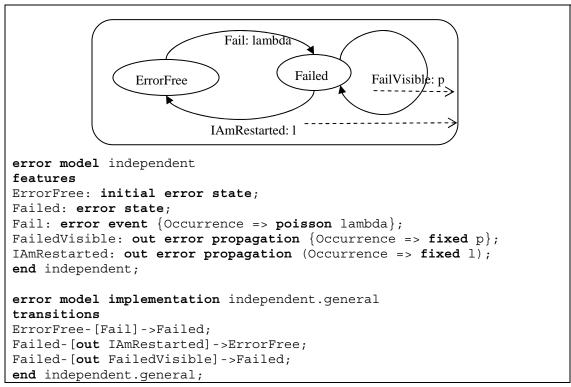

| Table 8:  | Error Model Definition with Error Observation               | 14 |

| Table 9:  | Error Model Definition for a Hardware Component             | 17 |

| Table 10: | Error Model for Software Component                          | 20 |

| Table 11: | Error Model Handling Behavior                               | 20 |

| Table 12: | Error Model Instance for Component Implementation           | 22 |

| Table 13: | Error Model Instance for Subcomponent                       | 22 |

| Table 14: | Shared Hardware Dependency Rules for Propagations           | 24 |

| Table 15: | Application Interaction Dependency Rules for Propagations   | 24 |

| Table 16: | Hardware Interaction Dependency Rules for Propagations      | 25 |

| Table 17: | Dependency Rules for Propagations to Address Special Cases  | 25 |

| Table 18: | Inheritance Rules for Error Propagation                     | 26 |

| Table 19: | Guard_In Property Use                                       | 29 |

| Table 20: | Error Propagation Mappings                                  | 31 |

| Table 21: | Masking and Filtering of Error Propagations                 | 32 |

| Table 22: | Guard_Out Property in Use                                   | 35 |

| Table 23: | Error Propagation Pass-Through Mappings                     | 37 |

| Table 24: | Guard_Out Example                                     | 39 |

|-----------|-------------------------------------------------------|----|

| Table 25: | Symmetry and Asymmetry between Guard_In and Guard_Out | 41 |

| Table 26: | Abstract Error Model Specified Using Model_Hierarchy  | 44 |

| Table 27: | Derived State Mapping Structure                       | 44 |

| Table 28: | Derived State Mapping Property                        | 47 |

| Table 29: | Guard_Event Property                                  | 51 |

| Table 30: | Event-Based Mode Transition Condition                 | 54 |

| Table 31: | Error-Based Mode Transition Condition                 | 56 |

| Table 32: | Activate and Deactivate State Transitions             | 57 |

| Table 33: | Cold Standby of a Self-Observing Component            | 59 |

| Table 34: | Hot Standby of a Self-Observing Component             | 61 |

| Table 35: | Self-Managing Component                               | 64 |

| Table 36: | Monitoring Component                                  | 66 |

| Table 37: | Mutually Informing Components                         | 68 |

| Table 38: | Mutually Observing Components                         | 70 |

| Table 39: | Error Model for Shared Repairman                      | 73 |

| Table 40: | Report Property                                       | 74 |

# **Abstract**

The Society for Automotive Engineers (SAE) recently published an Error Model Annex document (SAE AS-5506/1) to complement the SAE Architecture Analysis & Design Language (AADL) standard document (SAE AS5506) with capabilities for dependability modeling. The purpose of this report is to (a) explain the capabilities of the Error Model Annex and (b) provide guidance on the use of the AADL and the error model in modeling dependability aspects of embedded system architectures. The focus of the guidance is the creation of error model libraries and the instantiation of these error models on AADL architecture models. In that context, the report discusses modeling of error propagation, error filtering and masking, the interactions between error models and systems with operational modes, and modeling of repair activities.

# 1 Introduction

This report aims to show how the Error Model Annex [SAE-AS5506/1 2006] standard can be used in conjunction with the description capabilities of the Architecture Analysis & Design Language (AADL) standard [SAE-AS5506 2004] to add dependability-related information—such as fault and repair assumptions, error propagations, fault-tolerance policies, and voting—to an AADL architecture model. The resulting annotated model can then be used as an input to dependability analyses for fault forecasting during different phases of the development cycle.

Each dependability analysis requires specific dependability-related information from the model. This information may include

- · fault assumptions

- · repair assumptions

- fault-tolerance mechanisms

- stochastic parameters of the system (i.e., the occurrence of fault events and propagations)

- characteristics of phases in a phased-mission system

Depending on the analysis to be performed, the model will look different. For example, in the case of qualitative dependability analyses, no stochastic and timing properties are needed in the model. For a fault-tree analysis, repair assumptions do not need to be taken into account.

We assume that the reader is familiar with the concepts of fault-tolerance and dependability analysis. The reader is referred to the *Dependability Handbook* for detailed information on these topics [Arlat 1998]. This report is structured as shown in Table 1:

Table 1: Content in this Document

| Section | Description of Content                                                                                                                                                         |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2       | Presents the scope of the AADL Error Model Annex                                                                                                                               |  |

| 3       | Identifies the constructs of the AADL core language relevant to error modeling and comments on the level of architectural detail necessary for dependability-oriented modeling |  |

| 4       | Explains mechanisms for reusing error models                                                                                                                                   |  |

| 5       | Shows the architecture-dependent parts of the dependability-related information (i.e., the parts that cannot be reused across architectures)                                   |  |

| 6       | Presents hierarchic error modeling options                                                                                                                                     |  |

| 7       | Discusses issues related to dependability modeling for systems with operational modes                                                                                          |  |

| 8       | Explains how you can deal with maintenance and repair in AADL models                                                                                                           |  |

| 9       | Presents the mechanisms that allow you to specify elements in the model of interest to specific dependability analyses                                                         |  |

# 2 Dependability Modeling with the Error Model Annex

The Error Model Annex can be used to annotate the AADL model of an embedded system to support a number of the methods cited in SAE ARP4761, *Guidelines and Methods for Conducting the Safety Assessment Process on Civil Airborne Systems and Equipment* [SAE-ARP4761 1996]. An architecture specification containing error models may be subjected to a variety of analysis methods. For example, fault trees can be generated from specifications to assess safety, or Markov analyses can be applied to assess reliability and availability.

The error models of low-level components typically capture the results of failure modes and effects analysis (e.g., as failure modes and effects analysis as defined in SAE ARP 4761). The error models of the overall system and high-level subsystems typically capture the results of system hazard analysis (e.g., as hazard analysis as defined in SAE ARP 4761). Figure 1 illustrates the use of error models at different levels of the system hierarchy. Error models can also be associated with connections between components to characterize any fault behavior of component interactions, such as the transfer of data.

Figure 1: Error Models in System Hierarchy

The error behavior of a complete system emerges from the interactions between the individual component and connection error models. The system error model is a composition of the error models of its components where the composition is derived from the system hierarchy, the interactions between components, and the shared computing platform resources. For example, a component error model with probabilistic properties represents a stochastic automaton. The system error model represents the composition of the concurrent stochastic automata of the components in that system; it reflects error propagation between components based on the component dependencies in the AADL architecture model and the error management rules that are specified in error model annotations. Risk mitigation methods employed in embedded computer system architectures to increase safety, reliability, integrity, and availability are modeled by specifying how com-

ponents detect and mitigate errors in their subcomponents or in the components on which they depend.

The Error Model Annex supports mixed-fidelity modeling by annotating system components with different reusable error models. Mixed-fidelity modeling makes it easier to modify architecture specifications and automatically regenerate safety and reliability models at different levels of fidelity; it also enables improved traceability between architecture specifications and the generated models and analysis results.

You can define two kinds of reusable error models within an error model annex library: **basic error models** and **derived error models**. A basic error model declares a set of **error states** for a component or connection, together with **error state transitions** and properties to specify how the error state of a component changes due to **error events** and **error propagations**. For example, the error state of a component might change due to an internal fault, represented by an error event, or due to an error propagated into that component from some other component, represented by an error propagation.

In a derived error model, the **error state** of a component may be defined in terms of the error states of its subcomponents. For example, a component having internal redundancy might be in an erroneous state only when two or more of its subcomponents are in erroneous states. In this case, error state transitions are not explicitly defined.

You annotate application system components and execution platform components through **error model annex subclauses**. These subclauses specify an error model from the library to be used for a component and component-specific **properties** of the error model, such as

- probability of occurrence of errors and error propagation

- logical guards that determine the effects those errors and error propagations have on component error states

- mappings of error states and error propagations in the error model into events on event ports of components

- mode transition conditions in terms of events through event ports, error states, and error propagations

You may use a basic error model as an abstraction for a given subsystem; a derived error model should be specified in terms of subcomponent and connection error models of that subsystem.

It is possible to check for consistency, completeness, and traceability between the error models of interacting components and between the error models of components and their subcomponents. This monitoring capability helps ensure a globally consistent and complete error model for the overall architecture. It also enables an integrated approach that ensures consistency and completeness between hazard analysis (HA) and failure modes and effects analysis (FMEA) and with the safety and reliability analyses that associate them together.

# 3 The AADL Architecture Model

To perform dependability analyses, you can describe a system's architecture in AADL and annotate this architecture model with error models containing relevant dependability-related information. AADL supports modeling of the embedded software system, the hardware platform, and the external environment as a set of interconnected application components mapped onto a set of interconnected execution platform components.

For dependability analyses, the architecture model does not need to be complete (i.e., the software does not need to be modeled to the level of threads and the hardware does not need to be described in terms of memory, processors, devices, and buses):

- The application software can be modeled using AADL system components; it can also be modeled to the level of partitions or that of processes and threads.

- The hardware platform can be modeled using AADL system components, or it can be modeled to the level of processors, memory, devices, and buses.

- The component may be defined at different levels of abstraction. For example, an AADL

model with a real-time operating system or a bus type may represent a network including protocols. These execution platform component specifications can later be refined into models

that provide the details of the implementation.

- Dynamic aspects of system architecture can be captured with the AADL mode concept. Different modes of a system or system component can represent different system configurations and connection topologies, as well as different sets of property values to represent changes in nonfunctional characteristics such as performance or fault occurrence.

It is only necessary to model the components that are of interest in the analysis (i.e., those for which the behavior in the presence of faults is considered). As a result, architecture models can be formed at early stages in the development process, when the architecture is not completely detailed. Later, they can be refined into a more detailed architecture representation for higher fidelity analysis.

The scope of the dependability analysis determines the aspects of the system to be modeled in AADL. The model may focus on representing the computing platform and the external environment, the embedded application software system, and an embedded application deployed on a particular execution platform. In the last case, the binding of the application system to the execution platform is expressed in AADL through a set of binding properties.

AADL supports the representation of end-to-end flows through the concept of a flow specification. End-to-end flows can be analyzed in the context of partially or fully complete AADL models. This flexibility allows for flow-related analyses to increase in fidelity as the architecture model is refined. Although not explicitly referenced in the Error Model Annex standard, end-to-end flow specifications can identify the relevant system components needed to document critical flows that must be considered in a reliability, availability, or fault-tree analysis.

You can find detailed information about the architecture description capabilities of AADL in *The Architecture Analysis & Design Language (AADL): An Introduction* [Feiler 2006] and the AADL standard document [SAE-AS5506 2004].

# 4 Reusable Error Models

In this section, we describe how to define error models that can be applied to a number of system components and tailored with component-specific information (i.e., error models that are reusable). We also illustrate how to associate such an error model to a component and provide examples of reusable error models.

#### 4.1 ERROR MODEL DEFINITION

An error model is a state machine that can be associated with an AADL component or connection in order to describe its behavior in terms of logical error states in the presence of faults. Error models can be associated with (1) hardware components (processor, memory, device, and bus), (2) software components (process, subprogram, data, thread, and thread group), (3) composite components (system), and (4) connections.

An error model definition is divided into an error model type and an error model implementation. Elements declared in the error model type can be customized through component-specific properties, when an error model is associated with a component as an error model instance. Several error model implementations can correspond to the same error model type. Table 2 shows both an error model type declaration and an error model implementation declaration.

Table 2: Error Model Definition

```

error model Example1

features

ErrorFree: initial error state;

Failed: error state;

Fail, Repair: error event;

CorruptedData: out error propagation

{Occurrence => fixed 0.8};

end Example1;

error model implementation Example1.basic

transitions

ErrorFree-[Fail]->Failed;

Failed-[out CorruptedData]->Failed;

Failed-[Repair]->ErrorFree;

properties

Occurrence => poisson 1.0e-3 applies to Fault;

Occurrence => poisson 1.0e-4 applies to Repair;

end Example1.basic;

```

The **error model** type Example1 declares error states (i.e., ErrorFree and Failed), error events (i.e., Fault and Repair), and error propagations that can affect other components (i.e., CorruptedData). One **error state** (ErrorFree) is the initial state.

The **error model** implementation Example1.basic declares error transitions between states that are triggered by events and propagations. The **error model** instance is initially in the state ErrorFree. Due to a Fault error event, it becomes Failed. Then, after a Repair

error event it becomes ErrorFree again. While Failed, the component sends error propagations CorruptedData.

Both the error model type and the implementation can declare Occurrence **properties** for error events and error propagations. Occurrence **properties** specify the arrival rate (the language keyword is **poisson**) or occurrence probability (language keyword is fixed) of error events and outgoing error propagations. For the **poisson** arrival rate, the Occurrence property takes a single positive real value, which is the  $\lambda$  parameter in the exponential survival distribution  $1 - e^{-\lambda t}$ . For the fixed probability, the Occurrence property takes a single real value in the range [0.0, 1.0]. The Occurrence property can also have a user-defined distribution (indicated by the language keyword nonstandard and the distribution name) with one or more values. The Error Model Annex standard permits the Occurrence property to have literal expressions (i.e.,  $\mu$ ,  $\rho$ , or 1- $\rho$ ).

If both the error model type and the error model implementation declare Occurrence **properties** for a same error event or error propagation, the property value declared in the error model implementation overrides the one declared in the error model type. The value declared in the error model type can be seen as a default value while the value declared in the error model implementation can be seen as an implementation-specific value (i.e., different implementations corresponding to the same type can declare different values for the Occurrence property of a same error event or error propagation). Either of these values can be replaced by a component-specific Occurrence value for each of the components with which the error model is associated (see Section 5.1).

#### **Observations**

- Elements declared in an error model definition can have slightly different meanings according to the dependability analysis to be performed. For example, a state can represent a failure mode identified in an FMEA analysis or a hazardous state identified in a hazard analysis.

- Although called **error state**, states can represent error-free states as well as error states.

- Although called an error event, this logical event may represent a repair event as well

as a fault event.

- Some analyses do not involve probabilistic dependability measures; therefore, they do not

require the definition of occurrence properties (i.e., Occurrence property declarations are

optional).

- Note that error events and error propagations are logical events that may represent transient faults. They are not port events that are communicated through event ports. Error events can be declared in error models that can be associated with any kind of AADL component and connection, even with components that cannot communicate events through event ports. For example, one can associate an error model declaring error events and propagations with a memory component. Although memory components are not able to send events through ports, error events and states of the associated error model may be observed by the system; they may be mapped into port events (Guard\_Event) and may specify a condition for transition to a different operational mode (Guard Transition).

#### 4.2 ERROR MODEL ANNEX LIBRARIES

Error model definitions like the one shown in Table 2 are meant to be reusable. They are defined as error model annex libraries separately from AADL component types and component implementations.

An error model annex library is declared as shown in Table 3. Several error model definitions are declared between the constructs **annex** Error Model {\*\* and \*\*};.

Table 3: Error Model Annex Library

```

package My_ErrorModels

public

annex Error_Model {**

error model Example1

...

end Example1;

error model implementation Example1.basic

...

end Example1.basic;

error model Example2

...

end Example2;

error model implementation Example1.basic

...

end Example2.basic;

**};

end My_ErrorModels;

```

Error model annex library declarations can be placed in AADL packages or in the local (anonymous) namespace of an AADL specification. When declared in an AADL package, an error model can be referenced by the package name and the error model name from within error model annex subclauses of any component type or component implementation. When declared in the local namespace, the error model can be referenced by its name and can only be referenced within error model annex subclauses in component types and component implementations declared in the same local namespace.

#### Observations

- Different error models can be defined with the same name as long as the error model definitions are placed in different AADL packages.

- The AADL standard limits each AADL package to one annex library declaration for each annex. Consequently, all error model definitions in a package must be placed in the error model annex library declaration.

#### 4.3 EXAMPLES OF ERROR MODEL DEFINITIONS

This section includes some examples of error model definitions that could be placed in a library and then applied to and customized in AADL models. We first define a simple error model for an

isolated system component (i.e., a system component whose errors do not affect other components and that is not affected by errors of other components). In that context, we illustrate how to model faults and repairs as well as transient and permanent faults. We then define an error model for system components that propagate errors and are affected by propagated errors.

## 4.3.1 Fault and Repair Models for an Isolated Component

Table 4 shows a simple two-state error model definition that models faults in components. We refer to it as a **fault model**. It declares two error states, ErrorFree and Failed, and one error event, Fail. This error event triggers a transition between the two states. This error model definition does not declare any propagation, so it cannot influence the behavior of any components that interact with the component to which it is associated.

This fault model definition is simple for three reasons:

- It takes failure into account.

- 2. The behavior of any component in the presence of faults can be described in terms of the ErrorFree and Failed states.

- 3. It declares a literal Occurrence property value for events that represent faults, which can be tailored for each component.

Table 4: Fault Model Definition for Isolated Component

This error model can be extended to include repair behavior as a **fault and repair model**. For this model, we add an event to represent that a component can repair itself or be repaired. This repair event is then used to specify a transition from the Failed to the ErrorFree state. A fault and repair model is illustrated in Table 5.

Table 5: Fault and Repair Model Definition for Isolated Component

#### **Observations**

- Fault models can be used to represent fault information in dependency analyses that focus on faults, such as a fault tree analysis. The state machine represented by error states and error state transitions typically is without cycles (i.e., error events do not cause the error model to return to an error-free state). This allows the error model to be translated into fault trees.

- Fault and repair models can be used on system components that permit repair during the life of the system. Note that the state machine represented by error states and error state transitions is cyclical due to the fact that repair events may return the error model state to an error-free state. Fault tree analysis can still be performed, because the cycles of this state machine can be broken by distinguishing between fault events and repair events. To distinguish between event types, the error event should be tagged with a property (to indicate whether it is a fault or repair event) that can be interpreted by analysis tools.

# 4.3.2 Modeling Transient and Permanent Faults

Components, in particular hardware components, exhibit transient and permanent faults. Initially a component is in an ErrorFree state. Faults are activated with a specified rate, 1h. A fault is permanent with a given probability (ph) and temporary with the complementary probability (1-ph). Errors caused by temporary faults disappear after a short period of time (dh). These behaviors are illustrated in Table 6.

Table 6: Fault Model with Transient and Permanent Faults

### Observations

- We introduced an Activation\_Fault state that allows the specification of a probability of fault occurrence separately from the probability that the fault is a permanent versus a transient fault. The same model can be specified without that intermediate state, when the modeler specifies the occurrences of the permanent and transient faults as separate probabilities.

- We modeled the transient fault as persisting for a short period of time, reflected in the Transient\_Error state and the transitions between it and the ErrorFree state. If the modeler cares to model only the occurrence of a transient error, not its duration, the Transient\_Error can be eliminated, and a transition can be defined from the ErrorFree state to itself.

#### 4.3.3 Modeling Error Propagation

In many systems, failing components affect other components, because the components interact or one component is an execution platform resource that an application component is bound to for execution. Impact dependency information exists in an AADL model (see Section 5.2) and is used when the modeler specifies how errors are propagated and how propagated errors are handled for a system component (see Section 5.3).

In this section, we demonstrate how an error model shows that a component can propagate errors to other components and be affected by errors propagated from other components through **error propagations** (see Table 7). The error propagation property enhances the error model definition shown in Table 4 on page 9 by declaring error propagations and referring to them in error state transitions. The property declares outgoing and incoming propagations through an **in out** propagation declaration. The **in out** propagation declaration is a shorthand for declaring an **in** propagation and an **out** propagation with the same name.

An error propagation out of a component is specified with an **out** error propagation declaration. An **out** error propagation occurs spontaneously and randomly according to the specified occurrence probability, when it is named in an error state transition and the current error model state of the component is the origin of the transition.

An **in** error propagation indicates that a component knows the propagations coming from other components by the specified name. The mapping of **out** error propagations of one component to an **in** error propagation of an impacted component is determined by name matching or explicitly specified as propagation guards for specific system components (see Section 5). The **in** propagation can be named in an error state transition to indicate that any error propagated from another component results in a transition to the destination state of that transition declaration.

In Table 7, we can assume that a component failure influences the behavior of components that depend on it. We make this action visible through the error propagation FailVisible that occurs with a given probability p. The Occurrence property only applies to the FailVisible out propagation. In propagations are the consequences of out propagations from other components; therefore, they do not need Occurrence properties.

The two supplementary transitions declared in the **error model implementation** specify respectively that

- 1. If the component is in the state ErrorFree and receives a FailedVisible **in** propagation, it goes to the state Failed.

- 2. The component remains in the state Failed when propagating out the FailedVisible propagation.

Table 7: Error Model Definition for Component with Error Propagation

Table 8 shows an error model that models components that can observe failure of other components but their error state is not affected by error propagation. A component may fail and can be restarted to regain its ErrorFree state. Out propagations are used to notify when the component fails and when it is restarted.

Table 8: Error Model Definition with Error Observation

#### **Observations**

- In the models shown in Table 7 and Table 8, the Fail error event shows that a fault occurs in a component and is recognized as error. By defining a separate outgoing error propagation, we can represent that the error may not always be observed by another component or may be observed with a delay. We indicate those situations through an appropriate Occurrence property value of the error propagation.

- An error propagation reports an error state to other components. If their error states are affected, the other components will have a corresponding in propagation. Alternatively, those components may observe the out propagation through guards and take action based on the condition of the guard. (See Sections 5.4 and 5.5 for information about guards.)

- If the component fault is always and immediately visible to other components (i.e., the probability of occurrence of the propagation is 1), we could choose to declare Fail as an error propagation instead of an error event. However, the resulting error model would be less reusable because it includes an assumption that the failure is always visible.

- In general, the error state of a component is made visible to other components by declaring an error state transition that triggers an error propagation by naming an out propagation and has the same source and destination states (i.e., the propagation is sent out of the component but the component itself does not move to a different state). Figure 2 shows this mechanism. When the component is in StateA, it sends out an I\_Am\_In\_State\_A propagation and returns to StateA. It is noteworthy that the state is only visible if the out propagation occurs. If the out propagation occurs with a probability different from 1, the state may not be always visible.

Figure 2: State Visible from Outside

The error model definition in Table 7 on page 13 can be considered to be more practical than the one in Table 4 on page 9, because it assumes that the AADL component to which it is associated interacts with other AADL components. The error model definition in Table 7 is general enough to be applied to any AADL component.

We can represent a more realistic behavior in the presence of faults by distinguishing different kinds of faults and consequences, as well as error detection mechanisms. The specification of an error model definition depends directly on the fault and repair assumptions considered in a given system and operational scenario. In the two following sections, we present error model definitions intended to describe the behavior of hardware and software components, respectively.

#### 4.3.4 General Error Model for Hardware Components

In Figure 3, we define a general error model for hardware components. The behavior of the hardware component in the presence of faults is as follows:

- 1. Initially, the component is in HW ErrorFree state.

- 2. Hardware faults (error event HW\_Fault) are activated with a specified rate (1h) resulting in a transition to the HW\_Activation\_Fault state.

- 3. The fault is either permanent (error event HW\_Perm\_Fault), with a given probability (ph) triggering a transition to the HW\_Permanent\_Error state, or transient (error event HW\_Trans\_Fault), with the complementary probability (1-ph) triggering a transition to the HW Transient Error state.

- 4. The error caused by a permanent fault may be detected after some time (th), represented in Figure 3 as a transition triggered by error event HW\_Detection\_Action to the HW\_Detection\_Action\_End state.

- 5. An error caused by a permanent fault is either detected (HW\_Perm\_Fault\_Detect) with a given probability (dh) or not detected (HW\_Perm\_Fault\_Non\_Detect) with a probability (1-dh).

- If the error is detected, the hardware component is repaired as represented by the

HW In Repair state.

- If the error is not detected (represented by the HW\_Error\_Non\_Detect state), the failure is perceived after a certain amount of time (fph). This behavior is shown as error event HW\_Failure\_Perceived and triggers a transition the HW\_In\_Repair state, after which the hardware component is repaired.

- 6. The component repair from a permanent fault takes some time (muh), with a transition triggered by error event HW Repair Perm to the HW ErrorFree state.

- 7. An error caused by a transient fault disappears after a short period of time (tfh). This behavior is shown as a transition triggered by error event HW\_Repair\_Trans to the HW ErrorFree state.

Figure 3: General Hardware Component Error Model

Some of the hardware states may influence other components of the architecture. Therefore, they must be made visible to the outside through outgoing error propagations (shown in Figure 3 as dashed lines with arrows). We assume that this influence exists for

- the transient error state

- The transient error state is observed by other components after a certain amount of time (qh) as represented by the outgoing error propagation HW\_Transient.

- the state corresponding to a nondetected error

- The nondetected error state is observed by other components after a certain amount of time (rh) as represented by the outgoing error propagation HW\_Perm\_Non\_Detect.

- the state where the hardware component needs repair

- The state representing a hardware component needing repair is observed by other components after a certain amount of time (sh) as represented by the outgoing error propagation HW Failed.

Table 9 shows the error model definition corresponding to the specification depicted in Figure 3. Notice that we used the HW prefix for all error states, events, and propagations in order to ensure the readability of the model when several error models are associated with different system components. Also, propagation names are important, because **in** and **out** propagations declared in error model instances associated with interacting components are matched through their names or are named in guard specifications.

Table 9: Error Model Definition for a Hardware Component

```

error model forHardware

features

HW ErrorFree: initial error state;

HW Activation Fault, HW Transient Error, HW Permanent Error,

HW Detection Action End, HW Error Non Detect, HW In Repair: error

HW Fault: error event {Occurrence => poisson lh};

HW Perm Fault: error event {Occurrence => fixed ph};

HW_Trans_Fault: error event {Occurrence => fixed 1-ph};

HW Detection Action: error event {Occurrence => poisson th};

HW Failure Perceived: error event {Occurrence => poisson fph};

HW Perm Fault Detect: error event {Occurrence => fixed dh};

HW Perm Fault Non Detect: error event {Occurrence => fixed 1-dh};

HW Repair Trans: error event {Occurrence => poisson tfh};

HW Repair Perm: error event {Occurrence => poisson muh};

HW Transient: out error propagation {Occurrence => fixed qh};

HW Perm Non Detect: out error propagation {Occurrence=> fixed rh};

HW Failed: out error propagation {Occurrence => fixed sh}; end

forHardware:

error model implementation forHardware.general

transitions

HW ErrorFree-[HW Fault]-> HW Activation Fault;

HW_Activation_Fault-[HW_Trans_Fault]-> HW Transient Error;

HW Activation Fault-[HW Perm Fault] -> HW Permanent Error;

HW Transient Error - [HW Repair Trans] -> HW Err Free;

HW Permanent Error-[HW Detection Action] -> HW Detection Action End;

HW Detection Action End - [HW Perm Fault Detect] -> HW In Repair;

HW Detection Action End-[HW Perm Fault Non Detect] ->

HW Error Non Detect;

HW Err Non Detect-[HW Failure Perceived] -> HW In Repair;

HW In Repair-[HW Repair Perm]-> HW ErrorFree;

HW Transient Error - [out HW Transient] -> HW Transient Error;

HW Error Non Detect-[out HW Perm Non Detect]-> HW Error Non Detect;

HW In Repair-[out HW Failed]-> HW In Repair;

end forHardware.general;

```

The error model definition shown in Table 9 can be associated to a hardware component and then customized by using particular values for Occurrence parameters. This definition models the fault and repair assumptions presented by Figure 3. If you want to consider additional assumptions, you can modify the model. For example, you can assume that errors might become visible outside the component when the component is in the state HW\_Permanent\_Err\_State, even though the detection action has not taken place yet.

#### 4.3.5 General Error Model for Software Components

We can consider the following behavior in the presence of faults for a software component. The error model is shown in Figure 4.

- 1. Initially, the component is in SW ErrorFree state.

- 2. Faults (shown as error event SW\_Fault) are activated with a specified rate, ls, leading to an SW Activation Fault state.

- 3. The error detection mechanisms need some time to detect an error (represented by the error event SW\_Detect\_Action with distribution ts), culminating in an SW Detection Action End state.

- 4. An error can be detected (shown as error event SW\_Detected) with a given probability ds or not detected (shown as error event SW\_Non\_Detected) with the complementary probability 1-ds.

- 5. A detected error is processed during a certain amount of time (error event SW\_Handling with distribution pis), triggering a transition to the SW Handling End state.

- If the detected error is caused by a temporary fault (error event SW\_Error\_Temp with probability 1-ps), its effects would be eliminated by the error detection mechanisms.

Consequently, the component moves to the SW\_ErrorFree state. (Note: It is assumed that all temporary faults can be eliminated.)

- If the error is caused by a permanent fault (error event SW\_Error\_Perm with probability ps), the software would need to be restarted (SW\_In\_Restart state) to eliminate the effects of the error.

- 6. The effects of a nondetected error may disappear after a certain amount of time (error event SW\_Non\_Detected\_Disappear with distribution dis) or may be perceived after a certain amount of time (error event SW\_Non\_Detected\_Perceived with distribution pcs).

- 7. After recovery from a detected error due to a permanent fault or from a nondetected and perceived error, restart takes some time (error event SW Restart with distribution vs).

- 8. Other components may observe the malfunctioning of the software component after a certain amount of time, once the SW\_In\_Restart state is entered. This behavior is shown as an outgoing error propagation SW Failed.

Figure 4: General Software Component Error Model

Table 10 shows the error model definition corresponding to the specification illustrated by Figure 4. As we did for the hardware error model definition, we tagged all states, events, and propagations with an SW prefix.

Table 10: Error Model for Software Component

```

error model forSoftware

features

SW ErrorFree: initial error state;

SW Activation Fault, SW Detection Action End, SW Error Non Detected,

SW Error Detected, SW Handling End, SW In Restart: error state;

SW Fault: error event {Occurrence => poisson ls};

SW Detect Action: error event {Occurrence => poisson ts};

SW Detected: error event {Occurrence => fixed ds};

SW Non Detected: error event {Occurrence => fixed 1-ds};

SW Non Detected Disappear: error event {Occurrence => poisson dis};

SW Non Detected Perceived: error event {Occurrence => poisson pcs};

SW Handling: error event {Occurrence => poisson pis};

SW Error Temp: error event {Occurrence => fixed 1-ps};

SW Error Perm: error event {Occurrence => fixed ps};

SW Restart: error event {Occurrence => poisson vs};

SW_Failed: out error propagation {Occurrence => fixed ps};

end forSoftware;

error model implementation forSoftware.general

transitions

SW ErrorFree-[SW Fault]-> SW Activation Fault;

SW Activation Fault-[SW Detect Action] -> SW Detection Action End;

SW Detection Action End - [SW Detected] -> SW Error Detected;

SW Detection Action End -[SW Non Detected] -> SW Error Non Detected;

SW Error Non Detected-[SW Non Detected Disappear] -> SW ErrorFree;

SW Error Non Detected-[SW Non Detected Perceived] -

>SW In Restart; SW Error Detected-[SW Handling] -> SW Handling End;

SW Handling End - [SW Error Temp] -> SW ErrorFree;

SW Handling End - [SW Error Perm] -> SW In Restart;

SW In Restart-[SW Restart]-> SW ErrorFree;

SW In Restart-[out SW Failed] -> SW In Restart;

end forSoftware.general;

```

#### 4.3.6 Comparison of General Error Models for Hardware and Software Components

In the **error model** definitions shown in Table 9 and Table 10, we did not declare any **in** propagations because the matching between **in** and **out** propagations is done by matching names. Thus, we have to consider the architecture environment in order to choose names for **in** propagations. Section 5.1 shows how propagations are matched based on the AADL architecture model.

In the presence of faults, the error models for hardware and software components behave differently, as Table 11 shows.

Table 11: Error Model Handling Behavior

| Aspect                                                | Hardware Component Error Model                                                                                     | Software Component Error Model                                         |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| The point at which faults are distinguished           | Temporary and permanent faults are distinguished immediately following the fault activation during error handling. | Temporary and permanent faults are distinguished just prior to repair. |

| The result of permanent faults and perceived failures | Repair                                                                                                             | Restart                                                                |

# 5 System Architectures and Error Models

Using AADL, you can model systems as

- a hierarchical collection of interacting application system components

- a set of computing platform components

- a set of device components that represent the external environment

The application components are bound to the computing platform. Device components are logically connected to application components and physically connected to computing platform components.

Error models can be associated with application components, computing platform components, and device components, as well as with the connections between them. An error model associated with a component can be customized by setting component-specific values for the arrival rate or probability of occurrence for error events and error propagations declared in the error model type.

Interactions between the error models of different components are determined by interactions between components in the architecture model (i.e., connections and bindings). Out propagations are sent out of a component through all features connecting it to other components. Thus, out propagations have an effect on any receiving component that declares an in propagation with the same name.

You might need to model the handling of error propagations from multiple sources. In that case, you can use propagation filtering through voting mechanisms to control error propagations, which can be modeled by specifying filtering and masking conditions for propagations in an error model to a component.

In this section, we describe

- 1. how error models can be associated with components (Section 5.1)

- 2. the component dependencies through which errors can be propagated (Section 5.2)

- 3. error propagation across components in the context of a simple system model (Section 5.3)

- 4. the mechanisms to model masking and filtering of error propagations (Sections 5.4 and 5.5)

#### 5.1 ASSOCIATION OF ERROR MODEL INSTANCES

You can choose an error model definition and associate an instance of it with an AADL component. Error model instances are declared for system components or connections through the Model property in an error model annex subclause, as shown in Table 12. The Model property names the error model implementation to be used. If the error model definition is in a different package than the component, the package identifier precedes the name of the error model. The

error model is associated with any component that is an instance of the component implementation containing the Model property.

The Model property also allows you to define a new error model without placing it in an error model annex library. However, this option is not recommended, because the error model would not be reusable (i.e., it cannot be instantiated anywhere else).

You might define component-specific Occurrence properties for events and outgoing propagations declared in the error model type definition through the applies to error clause. This clause allows you to customize error models (i.e., to specify component-specific Occurrence properties for the same error model associated with several different components). In Table 12, we specify that computer.personal propagates corrupted data with a higher probability than the default specified as part of the error model type definition declared in the library. The applies to error clause associates a component implementation-specific Occurrence property value with the error event CorruptedData.

Table 12: Error Model Instance for Component Implementation

```

system computer

end computer;

system implementation computer.personal

annex Error_Model {**

Model => My_ErrorModels::Example1.basic;

Occurrence => fixed 0.9 applies to error CorruptedData;

**};

end computer.personal;

```

Error model property values can also be specified for specific instantiations of components (sub-component declarations) and connections (see Table 13). The **applies to** clause is used with a Model property to specify an error model instance for the CPU subcomponent. The **applies to** clause may specify a path to a subcomponent or connection (i.e., a dot-separated sequence of subcomponent names ending with a subcomponent or connection name to identify a component or connection recursively contained in the component implementation).

Table 13: Error Model Instance for Subcomponent

```

system computer

end computer;

system implementation computer.personal

subcomponents

CPU: processor Intel.DualCore;

RAM: memory SDRAM;

FSB: bus FrontSideBus;

annex Error_Model {**

Model => My_ErrorModels::Example1.basic applies to CPU;

Occurrence => fixed 0.9 applies to error CPU.CorruptedData;

**};

end computer.personal;

```

Similarly, the **applies** to error clause may specify a path to an error model feature of a sub-component or connection (i.e., a dot-separated sequence of subcomponent names ending with a

subcomponent or connection name and followed by the error model feature name). Table 13 shows the Occurrence property being associated with the CorruptedData error propagation of the CPU subcomponent.

#### Observations

- A component-specific Occurrence property value overrides values declared in the error model definition (type and implementation).

- Similarly, the applies to error clause can be used to declare all component-specific

Occurrence property values in the error model annex subclause of the system

implementation. Thus, component-specific and connection-specific error model information can be placed with either each component declaration or the root component of

the system.

#### 5.2 ERROR PROPAGATIONS BETWEEN COMPONENTS OF THE SYSTEM

Propagation of errors between components is determined by their interdependencies. Those dependencies are defined as **dependency rules** in the AADL architecture model and fall into four categories (see Section 5.2.1). A second set of rules, defined as **inheritance rules**, determine propagations when a component or connection does not have an error model (see Section 5.2.2).

## 5.2.1 Dependency Rules for Propagations

The first category of dependencies is **Shared Hardware Dependencies**; the rules in this category are due to the fact that application software components execute on hardware (see Table 14). The binding of the application components and connections to the execution platform components is specified through Actual\_Processor\_Binding, Actual\_Memory\_Binding, and Actual\_Connection\_Binding properties that indicate the processor, memory, bus, and device that application components and connections are bound to.

Similarly, the binding of a server subprogram call is specified through an Actual\_Subprogam\_Call\_Binding property and is treated as a connection in the dependency rules shown in (i.e., the remote call can be affected by the hardware over which the call is routed).

Table 14: Shared Hardware Dependency Rules for Propagations

| Rule No. | Propagations may occur from | Propagations may occur to                      |

|----------|-----------------------------|------------------------------------------------|

| D-1      | Processor component         | Every thread bound to that processor           |

| D-2      | Processor component         | Every connection routed through that processor |

| D-3      | Memory component            | Every software component bound to that memory  |

| D-4      | Memory component            | Every connection routed through that memory    |

| D-5      | Bus component               | Every connection routed through that bus       |

| D-6      | Device component            | Every connection routed through that device    |

The second category of dependencies is **Application Interaction Dependencies**. The rules in this category (see Table 15) are due to the fact that application components interact with each other through port-based communication (data ports, event ports, event data ports, and their respective connections), through access to shared data (provides and requires data access), and through calls on services provided by another component (server subprogram call bindings expressed through a Actual\_Subprogam\_Call property).

Table 15: Application Interaction Dependency Rules for Propagations

| Rule No. | Propagations may occur from | Propagations may occur to                                                                            |

|----------|-----------------------------|------------------------------------------------------------------------------------------------------|

| D-7      | Application component       | Each of the data components it has access to through provides and requires data access declarations  |

| D-8      | Shared component            | All components that access it to through provides and requires data access declarations <sup>1</sup> |

| D-9      | Application component       | Every connection from any of its out ports                                                           |

| D-10     | Connection                  | Every component having an in port to which it connects <sup>2</sup>                                  |

| D-11     | Application component       | Any component via its outgoing connections                                                           |

| D-12     | Client subprogram           | Every server subprogram to which a call is bound                                                     |

| D-13     | Server subprogram           | Every client whose calls are bound to that server                                                    |

The third category of dependencies is **Hardware Interaction Dependencies**; the rules in this category are due to the fact that execution platform components are connected to each other through shared access to buses (see Table 16). This is expressed in an AADL model by requires and provides bus access declarations and connections.

As a consequence of rules D-7 and D-8, an application component can affect any component with which it shares access to a data component. If read and write access properties are specified for data access, the flow of information can be taken into consideration in determining the impact.

As a result of rules D-9 and D-10, an application component can affect any connected component through its outgoing connections.

Table 16: Hardware Interaction Dependency Rules for Propagations

| Rule No. | Propagations may occur from | Propagations may occur to                                                |

|----------|-----------------------------|--------------------------------------------------------------------------|

| D-14     | Component                   | Each bus that is accessed by a component through a bus access connection |

| D-15     | Bus                         | Each component that accesses the bus through a bus access connection     |

As shown in Table 17, the fourth category of dependency rules addresses special cases in system architecture.

Table 17: Dependency Rules for Propagations to Address Special Cases

| Rule No. | Propagations may occur from | Propagations may occur to                                                                                                                                              |

|----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D-16     | Subcomponent                | Every other subcomponent of the same process                                                                                                                           |

| D-17     | Process                     | Every other process that is bound to any common processor or memory—except for processes that are partitioned from each other on all common resources                  |

| D-18     | Connection                  | Every other connection that is routed through any common bus, processor, or memory—except for connections that are partitioned from each other on all common resources |

| D-19     | Event connection            | Every mode transition that is labeled with an in event port that is a destination of that connection                                                                   |

Figure 5 illustrates propagation between error model instances based on application component interactions and execution platform bindings. The upper portion of the figure shows two components (A and B) connected by a port connection. Both the components and the connection have an error model instances. Error propagation occurs in the direction of the port connection flow. The lower portion of the figure illustrates that processors and the buses have error model instances as well. Error propagation can occur between these hardware components due to the bus connectivity. Finally, as the upward pointing arrows in Figure 5 show, error propagation can occur between the hardware and the application components and connections, due to their binding to the execution platform.

Figure 5: Execution Platform and Applications Error Propagation

# 5.2.2 Inheritance Rules for Propagations

A set of rules defines end-to-end error propagations (from one component error model to another one). These rules are designed to recognize that some AADL components will not have error model instances in a given architecture. Let us assume that a processor has an error model that declares out propagations but the threads bound to it do not have error model instances. In this case, no error model instance would be able to process those propagations. The set of inheritance rules for error propagation is shown in Table 18.

Table 18: Inheritance Rules for Error Propagation

| Rule No. | Inheritance Rule Text                                                                                                                                                                                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-1      | If the dependency rules define error propagations out of a component that does not have an associated error model but does have subcomponents with error models, then error propagations occur out of each subcomponent error model.                                                                  |

|          | Thus, where a component does not have an error model but its subcomponents do, error propagation occurs out of the subcomponents' error models and follows the dependency rules of the component.                                                                                                     |

| I-2      | If the dependency rules define error propagations out of a component that does not have an associated error model but does have a hierarchically containing component with an associated error model, then error propagations occur out of the error model associated with this containing component. |

|          | Thus, where a component does not have an error model but its parent does, error propagation occurs out of the parent error model.                                                                                                                                                                     |

| I-3      | If the dependency rules define error propagations in to a component that does not have an associated error model but does have subcomponents with error models, then error propagations occur into each subcomponent error model.                                                                     |

|          | Thus, where a component does not have an error model but its subcomponents do, error propagation is passed on to the error models of the subcomponents.                                                                                                                                               |

| I-4      | If the dependency rules define error propagations in to a component that does not have an associated error model but does have a hierarchically containing component with an associated error model, then error propagations occur into the error model associated with this containing component.    |

|          | Thus, where a component does not have an error model but its parent does, error propagation is handled by the parent error model.                                                                                                                                                                     |

| I-5      | If the dependency rules define error propagations in to a semantic connection, then propagations occur to all ultimate destinations of that connection.                                                                                                                                               |

|          | Thus, where a connection does not have an error model, error propagation is passed from the component that is the origin of the connection to the component that is the destination.                                                                                                                  |

| I-6      | If the dependency rules define error propagations in to a shared data component, then propagations occur to all other components that also share access to that data component.                                                                                                                       |

| I-7      | Errors never propagate from an error model instance to itself.                                                                                                                                                                                                                                        |

### 5.3 ERROR PROPAGATION ACROSS ERROR MODELS

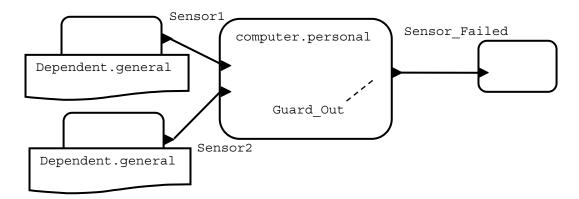

Let us assume that we have the following AADL architecture model: two system components are connected through a unidirectional data port connection that goes from Component1 to Component2, as shown in Figure 6. We assume that the behavior of Component2 depends on that of Component1, because Component2 receives data from Component1. We also assume that the connection is perfect (i.e., it never fails). We associate error models to Component1 and Component2, choosing to associate the same generic error model to both components, dependent.general as introduced in Table 7 on page 13.

Figure 6: End-to-End Propagation

We can apply the dependency and inheritance rules from Sections 5.2.1 and 5.2.2 to the AADL model of Figure 6. Specifically, rules D-9, D-10, and I-5 apply to this architecture. Component1 can propagate errors into the connection, and the connection can propagate errors into Component2. Also, propagations that go into a connection affect the ultimate destination of that connection if the connection itself does not have an error model instance. Consequently, outgoing propagations defined in the error model dependent .general and associated with Component1 can affect the error model dependent .general associated with Component2, as the error model dependent .general declares incoming propagations whose names match those of the outgoing propagations. The name matching rule does not apply if a Guard In condition is defined for an incoming propagation (see Section 5.4).

In short, due to the port connection from Component1 to Component2, errors are propagated from the error model of Component1 to the error model of Component2. Because port connections are directional, an error cannot be propagated from Component2 to Component1 unless there is also a port connection from Component2 to Component1—even though the error model of Component2 declares outgoing propagations that match incoming propagations in the error model of Component1.